# Implementation of SVPWM estimation technique for three phase VSI

<sup>[1]</sup> Priyanka. Ashok, <sup>[2]</sup> Reshma. Verma <sup>[1][2]</sup> Dept. of electronics and communication engineering <sup>[1][2]</sup> Ramaiah Institute of technology, Bengaluru, India

*Abstract* - In most of the applications to get the variable voltage and frequency for AC drives is obtained from Voltage Source Inverter. This paper exhibits the estimation of a space vector PWM (SVPWM) utilizing MATLAB/Simulink and ModelSim tools. Both the programs work in co-simulation mode provided by the Link- for-ModelSim toolbox in the Simulink. The choice of a particular PWM depends on the permissible harmonic content in the output voltage waveform. The simulation results showed that the technique preserves the advantage of the SVPWM especially with regard to the reduction of THD.

Index Terms— SVPWM; three phase VSI; MATLAB/simulink; Modelsim

## **I.INTRODUCTION**

As a result of advancement in solid state power electronic devices, switching power converters are used to a greater extent in modern motor drives to convert and distribute the required energy to the motor. Voltage source inverters are used in a lot of industrial applications such as UPS, frequency converters, motor drive. The crucial function of VSI is to synthesize AC output voltage and frequency from a constant DC voltage as a means of PWM technique. The main complications faced by the power electronic design engineers are about the reduction of harmonic content in inverter circuits. The choice of a particular PWM relies on the permissible harmonic content in the output voltage waveform, dc bus utilization and minimum switching losses. In recent years, there is an increase trend of utilizing SVPWM because of easy digital implementation and efficient utilization of DC bus voltage. [1] The SVPWM algorithm is the most complex, advanced PWM generation technique for three phase VSI in order to generate PWM gating signals for control of various AC motors, Because of its ability to generate inverter's wave output with variable amplitude for the same DC bus and its ability to reduce the harmonics and switching losses. This makes SVPWM the most widely accepted modulation technique. The comparative analysis between DSP's and FPGA based control capabilities in PWM converters in [10] concludes FPGA as a rival technology.With FPGA based implementation field programmable capability, flexible adjustment of dead time and switching frequency makes it suitable to drive various switching devices in practical application. In [5]author proposed a Universal

SVM with dead time compensation and over modulation is not a flexible design and its switching frequency cannot be set arbitrarily. In [2] the authors implemented SVPWM and ANN-SVPWM. The mathematical complexity involved with SVPWM is reduced extremely but the design of an ANN is an iterative process, and based on the application and nonlinearity suspected it is selected the ANN structure. The author in [3] proposed a comparison between the implementation of SPWM and SVPWM modulation techniques for controlling a three-phase inverter to find the simplicity of the algorithm and compare the overall performance of both the techniques. Related to the area of control and power electronics [6][8][13] demonstrate how the researchers are working on reconstructing PWM techniques. In this article, a new SVPWM estimation technique is proposed which shows the approximate reduction in total harmonic distortion. The SVPWM generated gating signal waveforms is given to the three phase VSI. This work focuses on design of this block using HDL (VHDL/verilog) so, that the software control can be transferred to FPGA kit. The HDL block models are estimated using co-simulation with Modelsim and simulink/MATLAB. The inverter is modeled using Simulink. The rest of the paper is organized as follows: section 2 discusses the theory of generation of SVPWM, section 3 shows the simulation results of SVPWM pulses generated and output voltages of inverter, section 4 ends with conclusion.

### **II . GENERATION OF SVPWM**

### A. Voltage source inverter :

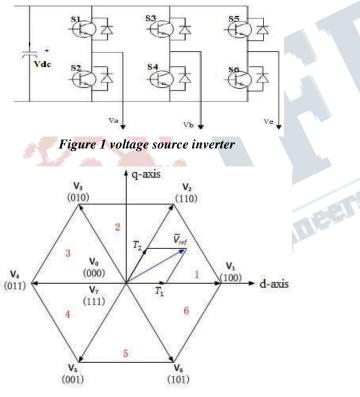

The three phase output voltage can be acquired from combination of six transistors i.e, VSI. The circuit model of a typical three phase VSI is as shown in the

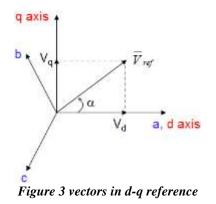

Figure 1. There are six power switches (S1-S6) that shape the output. There is assumption that the switching of these switches are in a complementary way. Since there are three leg, total 8 switching vectors are possible (V0-V7). Six out of these 8 vectors produce Non-zero switching voltage i.e, Nonzero switching states. The remaining 2 vectors produce zero output voltage i.e, zero switching states. Hence, the inverter output is composed of these eight switching states. Now, the Non-zero output voltage divide the space vector plane into 6 sized sectors of 60<sup>°</sup> with equal magnitude thus forming a origin centered hexagon, and the 2 zero vectors are at origin and the various possible switching vectors are as shown in Figure 2. The maximum boundary of space vector is hexagon. A Voltage reference (Vref) is provided in terms of a revolving space vector.

Figure 2 Switching sectors

### B. Principle of SVPWM :

The space vector pulse width modulation is inherently a voltage control scheme, calculates the optimum switching pattern for the three phase inverter. The calculations are performed in a d-q /space vector plane.

Realization of SVPWM involves the following steps:

### i. Co-ordinate transformation :

The three phase voltage equations in reference frame are transferred into the stationary d-q frame as shown in Figure 3. The relation between switching variable vector and phase voltage vector [Va Vb Vc] can be expressed as follows

$$V_{d} = V_{an} - V_{bn} \cdot \cos 60 - V_{cn} \cdot \cos 60$$

$$= V_{an} - \frac{1}{2} V_{bn} - \frac{1}{2} V_{cn}$$

$$V_{q} = 0 + V_{bn} \cdot \cos 30 - V_{cn} \cdot \cos 30$$

$$= V_{an} + \frac{\sqrt{3}}{2} V_{bn} - \frac{\sqrt{3}}{2} V_{cn}$$

$$\therefore \begin{bmatrix} V_{d} \\ V_{q} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} V_{an} \\ V_{bn} \\ V_{cn} \end{bmatrix}$$

$$\left| \overline{V}_{ref} \right| = \sqrt{V_d^2 + V_q^2}$$

$$\alpha = \tan^{-1}(\frac{V_q}{V_d}) = \omega_s t = 2\pi\pi_s t$$

(where,  $f_s = fundamental$  frequency)

*ii. Determine time duration T1, T2, T0 :* Consider sector 1. The vector states V0, V1, and V2 are to be switched ON for time durations T0, T1 and T2, respectively. Hence, for the switching time durations at Sector 1,

$$\begin{split} & \prod_{0}^{T_{1}} \overline{V}_{ef} = \int_{0}^{T_{1}} \overline{V}_{1} dt + \int_{T}^{T_{1}+T_{2}} \overline{V}_{2} dt + \int_{T_{1}+T_{2}}^{T_{1}} \overline{V}_{0} \\ & \therefore T_{z} \cdot \overline{V}_{\pi f} = (T_{1} \cdot \overline{V}_{1} + T_{2} \cdot \overline{V}_{2}) \\ & \Rightarrow T_{z} \cdot \left| \overline{V}_{ef} \right| \cdot \left[ \frac{\cos(\alpha)}{\sin(\alpha)} \right] = T_{1} \cdot \frac{2}{3} \cdot V_{de} \cdot \left[ \frac{1}{0} \right] + T_{2} \cdot \frac{2}{3} \cdot V_{de} \cdot \left[ \frac{\cos(\pi/3)}{\sin(\pi/3)} \right] \\ & \quad (\text{where, } 0 \le \alpha \le 60^{\circ}) \end{split}$$

$$T_1 = T_z \cdot a \cdot \frac{\sin(\pi/3 - \alpha)}{\sin(\pi/3)}$$

$$T_2 = T_z \cdot a \cdot \frac{\sin(\alpha)}{\sin(\pi/3)}$$

$$T_0 = T_z - (T_1 + T_2), \quad \left( \text{where,} \quad T_z = \frac{1}{f_z} \quad \text{and} \quad a = \frac{\left|\overline{V}_{ref}\right|}{\frac{2}{3}V_{de}} \right)$$

Similar calculations can be performed at any of the sectors to determine the suitable time combinations of vectors in any of the sectors

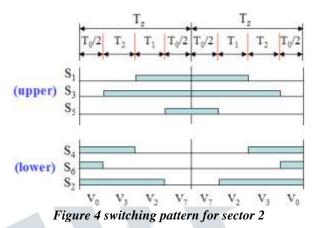

# iii. Determine the switching time of each transistor (S1 to S6):

Depending upon the sector, the time duration for which each switch is ON is determined, as shown in table 1. This time corresponds to the gating pulses given to each of the six IGBT switches. The sequence maintained is such, that only one switch changes state (from OFF to ON or vice versa) at a time, therefore minimizing the switching losses.

| Sector | Upper Switches (S <sub>1</sub> , S <sub>2</sub> , S <sub>3</sub> )                                                          | Lower Switches (S4, S5, S2)                                                                                        |

|--------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 4      | $S_1 = T_1 + T_2 + T_0/2$<br>$S_3 = T_2 + T_0/2$<br>$S_5 = T_0/2$                                                           | $\begin{array}{l} S_4 \equiv T_0 \ /2 \\ S_6 \equiv T_1 + T_0 \ /2 \\ S_2 \equiv T_1 + T_2 + T_0 \ /2 \end{array}$ |

| 2      | $\begin{array}{l} S_1 = T_5 + T_0 / 2 \\ S_2 = T_1 + T_2 + T_0 / 2 \\ S_5 = T_0 / 2 \end{array}$                            | $\begin{array}{l} S_4 = T_2 + T_4 \ /2 \\ S_5 = T_6 \ /2 \\ S_2 = T_1 + T_2 + T_0 \ /2 \end{array}$                |

| 3      | $\begin{array}{l} S_1 = T_0 / 2 \\ S_2 = T_1 + T_2 + T_0 / 2 \\ S_1 = T_2 + T_0 / 2 \end{array}$                            | $\begin{array}{l} S_4 = T_1 * T_2 * T_0 / 2 \\ S_8 = T_0 / 2 \\ S_7 = T_1 + T_0 / 2 \end{array}$                   |

| 4      | $\begin{array}{l} S_{1} \equiv T_{0}/2 \\ S_{3} \equiv T_{1} + T_{0}/2 \\ S_{5} \equiv T_{1} + T_{2} + T_{0}/2 \end{array}$ | $\begin{array}{l} S_4 = T_1 + T_2 + T_0 / 2 \\ S_8 = T_2 + T_8 / 2 \\ S_7 = T_8 / 2 \end{array}$                   |

| 5      | $S_1 = T_2 + T_0/2$<br>$S_3 = T_0/2$<br>$S_5 = T_1 + T_2 + T_0/2$                                                           | $\begin{array}{l} S_4 \equiv T_1 + T_0 \ /2 \\ S_8 \equiv T_1 + T_2 + T_0 \ /2 \\ S_2 \equiv T_0 \ /2 \end{array}$ |

| 6      | $S_1 \equiv T_1 + T_2 + T_0/2$<br>$S_3 = T_0/2$<br>$S_5 = T_1 + T_0/2$                                                      | $\begin{array}{l} S_4 = T_0 / 2 \\ S_4 = T_1 + T_2 + T_0 / 2 \\ S_2 = T_2 + T_0 / 2 \end{array}$                   |

# Table 1 SWITCHING TIME CALCULATION FOREACH SECTOR

| Table 2 | Outpu | t voltages | of three | e phase | inverter |

|---------|-------|------------|----------|---------|----------|

|---------|-------|------------|----------|---------|----------|

| Voltage        | Switching Vectors |     |   | Line to neutral voltage |      |      | Line to line voltage |                 |    |

|----------------|-------------------|-----|---|-------------------------|------|------|----------------------|-----------------|----|

| Vectors        | 8                 | b   | c | V <sub>n</sub>          | Va   | Va   | Vak                  | V <sub>kr</sub> | V  |

| Vo             | 0                 | 0   | 0 | 0                       | 0    | 0    | 0                    | 0               | 0  |

| V <sub>t</sub> | 10                | 0   | 0 | 2/3                     | -1/3 | +1/3 | 3                    | 0               | -1 |

| ¥2             | 1                 | 1   | 0 | 1/3                     | 1/3  | -2/3 | 0                    | Ť.              | 4  |

| V <sub>3</sub> | 0                 | 1   | 0 | -1/3                    | 2/3  | -1/3 | -1                   | 1               | Ó  |

| V4             | 0                 | t   | 1 | -2/3                    | 1/3  | 1/3  | ন                    | 0               | ্ৰ |

| Vs             | 0                 | 0   | 1 | -1/3                    | -1/3 | 2/3  | 0                    | -1              | 1  |

| Ve             | 1                 | 0   | 1 | 1/3                     | -2/3 | 1/3  | 1                    | -1              | 0  |

| ¥7             | ÷                 | - T | 1 | 0                       | 0    | 0    | 0                    | 0               | 0  |

## **III SVPWM ESTIMATION**

In this section the estimation of the SVPWM algorithm is presented. In this work direct polynomial relations have been developed between each reference voltage and conduction time period within the converter's arms.

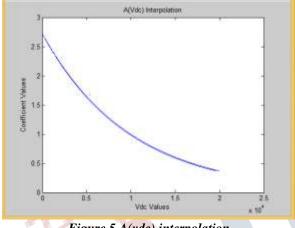

The conduction time duration can be obtained by the three first order polynomials (Va, Vb, Vc) and the one third order polynomials (Vdc).

$$Ton_{a,b,c} = A(V_{dc})V_{a,b,c} + k$$

Here, polynomial A is a function of DC bus voltage. A is constant if Vdc is constant and k is a constant. A is acquired to minimize the harmonic distortion by varying the dc bus voltage A(Vdc) interpolation graph

is as shown in the figure 5. A(Vdc) is a polynomial of order 3 given by the following equation.

$$A = a * V_{dc}^{3} + b * V_{dc}^{2} + c * V_{dc} + d$$

This equation can further optimally implemented by factorization.

$$A = \left( (a * V_{dc} + b) * V_{dc} + c \right) * V_{dc} \cdot + d$$

Hence, this estimation can consume six multipliers and six adders to calculate six switching times of switches.

Figure 5 A(vdc) interpolation

# IV SIMULATION RESULTS

In this work, the effectiveness of the proposed technique is proven by various simulation results. SVPWM algorithm is described in HDL performing all SVPWM calculation: coordinate the transformation, sector determination, switching time calculations, and switching signal generation. The three phase VSI has been described using Simulink. Implementation is done with a word length equal to 8 bits. The MATLAB allows performing the dynamics of system while the ModelSim runs a program written in HDL Figure 5 shows the SVPWM generated signals using ModelSim for sector 2 which is as expected with respect to theoretical result as shown in Figure 4. Figure 6 shows the line and phase voltages of three phase inverter. Figure 7 shows the harmonic's spectrum of the inverter output voltages. Table 3 and 4 shows the tabulation of THD for line and phase voltages. In practice, filters are added to filter the harmonics.

Figure 6 SVPWM for sector 1

Figure 7 line voltage of inverter

Figure 8 phase voltage of inverter

## Table 3 THD for phase voltages

| Phase voltages | Fundamental(50hz) | THD(%) |

|----------------|-------------------|--------|

| Van            | 229.9             | 52.75  |

| Vbn            | 229.8             | 52.68  |

| Vcn            | 230               | 52.67  |

Figure 9 Harmonic spectrum of phase voltage (Phase A)

Figure 10 Harmonic spectrum of line voltage (Phase A)

| line voltages | Fondamental(50hz) | THD(%) |  |

|---------------|-------------------|--------|--|

| Vab           | 398.1             | 52.75  |  |

| Vbc           | 398.4             | 51.60  |  |

| Vca           | 398.0             | 50.33  |  |

# Table 4 TDH for line voltages

## **V** CONCLUSION

This paper presents the realization of a SVPWM using HDL. The verification of algorithm is performed using co-simulation between ModelSim and Simulink. Simulation is a mandatory step in the design process of a power converter. This work presents the simulation of a DC-AC converter. The simulation result preserves the advantage of SVPWM especially with regard to the reduction of THD. The synthesis results would show that this new technique consumes few resources during implementation leaving enough resources for control loops implementation.

Future work includes extending the estimation technique to multilevel inverter as, the number of voltage level reaches infinity, the output total harmonic distortion approaches to 0.

### ACKNOWLEDGMENT

I would like to thank Reshma.Verma for guiding and supporting me throughout my work towards implementing of SVPWM estimation technique. I would also like to thank all the faculty members of the ECE Department of Ramaiah Institute of technology for supporting me during my project work.

#### REFERENCES

[1] Salim Boukaka; Hicham Chaoui; Pierre Sicar "FPGA implementation of SVPWM" Conference on Design of Circuits and Integrated Systems (DCIS), 2015

[2] J. Osorio; P. Ponce; A. Molina "FPGA-based space vector PWM with Artificial Neural Networks" 9th International Conference on Electrical Engineering, Computing Science and Automatic Control (CCE) Pages: 1 – 6, 2012

[3] Aishanou osha rait; praveen bhosale "FPGA implementation of space vector PWM for speed control of 3-phase induction motor," International conference on Recent advancements in Electrical, Electronics and control engineering, pp. 221-225, 2011.

[4] Chaurasiya Rohit B.; Mukesh D. Patil; Divya Shah; Abhijit Kadam "FPGA implementation of SVPWM control technique for three phase induction motor drive using fixed point realization" International Conference on Circuits, Systems, Communication and Information Technology Applications (CSCITA) 2014

[5] Z. Zhou, T. Li, T. Takahashi, and E. Ho "Design of a Universal Space Vector PWM Controller Based on FPGA," Nineteenth Annual IEEE Applied Power Electronics Conference and Exposition, APEC '04, Vol. 3, pp. 1698-1702, 2004.

[6] G.Renukadevi; K.Rajambal"FPGA implementation of SVPWM techniq ue for asymmetrical six-phase VSI "International Conference on Emerging Trends in Electrical Engineering and Energy Management (ICETEEEM), Pages: 333 – 338, 2012

[7] Xuexiu Liang; Min Luo; Bo Zhao; Yanwei Yuan; Zhi Chen " Research and implementation of SVPWM control algorithm based on FPGA" 2016 IEEE International Conference on Mechatronics and Automation Pages: 22 - 26, 2016

[8] Zhou Yuan, Xu Fei-peng and Zhou Zhao-yong "Realization of an FPGA-Based Space-Vector PWM

## International Journal of Engineering Research in Electronics and Communication Engineering (IJERECE) Vol 4, Issue 8, August 2017

Controller," Power Electronics and motion Control Conference, IPEMC'06, Vol. 1, pp. 1-5, 2006.

[9] O. Lopez, J. Alvarez, J. Doval-Gandoy and F.D. Freijedo "Multilevel Multiphase Space Vector PWM Algorithm," IEEE Transactions on Industrial Electronics, Vol. 55, No. 5, pp. 1933-1942, 2008.

[10] Zoghlami Maha; Bacha Faouzi "Implementation of Space Vector modulation using DSP" International Conference on Electrical Engineering and Software Applications, Pages: 1 - 7, 2013

[11] T. Lifanf, "Study of the SVPWM Converter Based on TMS320F24X," Third international Conference on Intelligent System Design and Engineering Applications, pp. 1316-1319, 2013

[12] Yingnan Wang and U. Schaefer, "Real time simulation of a FPGA based space vector PWM controller," Power Electronics electrical Drives Automation and Motion, pp. 833–838, 2010

[13] P. Thirumurugan, P.S. Manoharan, M. Valanrajkumar "VLSI based space vector pulse width modulation switching control," IEEE International Conference on Advanced Communication Control and Computing Technologies, ICACCCT, pp. 338-342, 2012.

[14] R. Cordero, J. Pinto and J. De Soares, "New Simplification of SVPWM based on conditional of the reference vector," IEEE International Power Electronics Conference, pp. 2992–2999, 2