ISSN (Online) 2394-6849

### International Journal of Engineering Research in Electronics and Communication Engineering (IJERECE) Vol 4, Issue 5, May 2017

# Review on Implementation of ALU using reversible logic gates and Vedic Mathematics

<sup>[1]</sup> Deepthi R Shetty, <sup>[2]</sup>, Ashwath Rao

<sup>[1]</sup>M.Tech VLSI Design and Embedded Systems, <sup>[2]</sup> Associate Professor Department of ECE

Sahyadri College of Engineering and Management, Adyar Mangalore, India.

*Abstract:* Arithmetic and logic unit (ALU) is a part of central processing unit that carries out arithmetic and logical operations and consists of many computational units like adders, multipliers, logic unit etc. In this review paper, ALU based on reversible logic gates and Vedic Mathematics concepts are discussed. Here reversible logic gates are used instead of the basic logic gates such as AND, OR etc which will function in the same way as that of the basic logic gates. An important requirement of digital system is to reduce power dissipation. By using reversible ALU instead of using basic logic gates power consumption is lowered. Also a high speed 8x8 bit multiplier based on Vedic multiplier mechanism is explained.

Keywords: ALU, FPGA, reversible logic, VedicMathematics, Xilinx ISE 14.1

#### I. INTRODUCTION

Power dissipation is a limiting factor that can be reduced with the help of using reversible logic. Power dissipation in very large scale integration (VLSI) systems is very high because of the rapid switching of internal signals and also the systems designed using conventional circuits dissipate heat due to loss of information bits during computation. Energy dissipation is proportional to the number of bits lost during computation. Reversible ALU reduces the information bits and hence we can lower the power consumption. In reversible circuits, the information bits are not lost and also it can generate unique outputs from specified inputs and vice-versa.

A Vedic Mathematics is another concept that is more efficient than the conventional method for performing the various mathematical computations. The use of Vedic Mathematics concepts in computation algorithm of a processor will reduce the complexity of area, the execution time, and power consumption etc. Urdhva-Tiryakbyham is the general formula which is applicable to all the cases of

multiplication and also in the division of a large number by another large number. Urdhva-Tiryakbyham Vedic method is used for eliminating unwanted multiplication steps with zeros and scaled to higher bit level and used to build high speed power efficient multiplier in a processor.

#### **II. RELATED WORK**

Landauer [1] proposed a design that showed loss of information bits results in dissipation of KT\*ln2 J of heat energy where K is Boltzmann constant and T is temperature. For example the AND gate, has two inputs and one output,

one bit is lost when the information bits go through this gate. For every bit of information loss, it will generate KT\*ln2 joules of heat energy. Bennett [2] showed that loss of information bits can be reduced by using reversible logic circuit. Viswanath and Ponni [3] implemented using reversible logic gate and its performance was analyzed. Rahul Nimje et al. [4] proposed ALU design using Vedic Mathematics techniques. Here processor load is reduced by connecting the main processor with coprocessor which is designed to function like numeric computation, image processing and arithmetic operation. Abhishek Gupta [5] has proposed an ALU design which performs three arithmetic operations eight different logical operations at high speed. S.P.Pohoker et al. [6] proposed ALU design using Vedic Mathematics method.

Here multiplication steps are reduced which in turn reduces the propagation delay and thus reduces hardware complexity. Abhyarthana Bisoyil et al. [7] proposed an ALU design with binary multipliers, where addresses are used in the design and development of ALU. The aim of this paper was to implement digital multipliers based on the concept of Vedic Mathematics. In order to design a digital multiplier, Urdhva-Tiryakbyham sutra of Vedic

Mathematics is used.

#### III. THE ARITHMETIC LOGIC UNIT (ALU) BASED ON REVERSIBLE LOGIC GATES

#### 3.1 8-Bit Adder/Subtractor

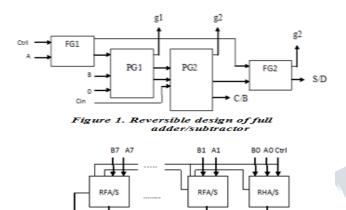

The reversible full adder/subtractor [8] is realized using Peres Gate [9] and Feynman gates [10] as shown in Figure 1,

## International Journal of Engineering Research in Electronics and Communication Engineering (IJERECE)

Vol 4, Issue 5, May 2017

where Ctrl, A, B and Cin are the inputs and S/D and C/B are the outputs of the adder/subtractor unit. Addition is selected by assigning the Ctrl value as zero and the Ctrl value as 1 for subtraction. Signals g1, g2 and g3 are the garbages of the unit. The 8-bit reversible ripple carry adder/subtractor is designed by placing the adder units as shown in Figure 2.

S D1

S DO

#### 3.2 8-Bit Multiplier

S D67

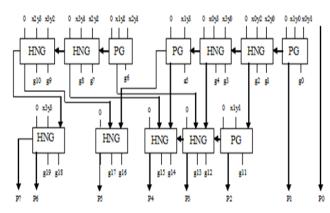

HNG gates [11] and Peres gate are used to perform multiplication and has two phases. In first phase partial products are generated in parallel. The output contains both partial products and garbages. In the second phase addition of partial products is done using reversible half-adder and fulladder gates constructed using the PG and HNG gate as shown in Figure 3 and the product P for inputs x and y is obtained.

Figure 2. Design of 8-bit adder/subtractor.

Figure 3. 8-Bit multiplication.

#### 3.3 Logical Unit

The basic logical operations included in this unit are AND, OR, NOT, NAND, NOR, XOR. The AND and OR gates are realized using the Fredkin gate [12]. The XOR and NOT operations are realized using Feynman gate. The NAND and NOR gates are realized using the new gate.

# 4. The Arithmetic Logic Unit (ALU) based on Vedic Mathematics

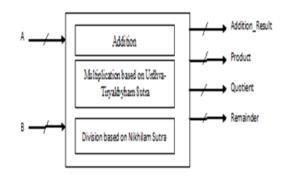

Figure 4 shows the block diagram of Vedic Mathematics based ALU design. The latches are used to store the two binary inputs and output result of an arithmetic or logic operation. The multiplexer is used to route the result of a selected operation to the output latches.

Figure 4. Block diagram of the Vedic Mathematics based ALU

Figure 5. Block diagram of arithmetic unit of the ALU

#### International Journal of Engineering Research in Electronics and Communication Engineering (IJERECE)

Vol 4, Issue 5, May 2017

Figure 5 is the block diagram for implementation of the Vedic Mathematics based arithmetic unit of the ALU. The addition is carried out using robust adders. The multiplication is carried out by using the Urdhva-Tiryakbyham Sutra. The Urdhva-Tiryakbyham Sutra is used to construct 2x2 multiplier blocks. Several such 2x2 multipliers along with ripple carry adders are used to design 4x4 multiplier blocks. This procedure is repeated to obtain the higher order multiplier blocks. The 8-bit Vedic Mathematics based arithmetic unit of ALU includes adder, subtractor, multiplier, divider and the logic unit.

#### **IV. CONCLUSION**

Design and implementation of ALU with reversible logic gates done in high level hardware description language, synthesized using EDA tool and implemented on Xilinx Spartan-6 is presented. ALU implementation using reversible logic gates showed 39% reduction in power dissipation when compared to the implementation using basic gates. ALU implementation using Vedic Mathematics concept showed lower power dissipation as compared to ALU implemented using basic gates.

#### REFERENCES

[1] R. Landauer, Irreversibility and heat generation in the computing process, IBM Journal of Research and Development, 5(3), 1961, 183–191.

[2] C.H. Bennett, Logical reversibility of computation, IBM Journal of Research and Development, 17(6), 1973, 525–532.

[3] L. Viswanath and M. Ponni, Design and analysis of reversible ALU, IOSR Journal of Computer Engineering (IOSRJCE), 1(1), 2012, 46–53.

[4] Rahul Nimje, Sharda Mungale, "Design of arithmetic unit for high speed performance using Vedic mathematics, International Journal of Engineering Research and Applications, April 2014, pp 26 – 31.

[5] Abhishek Gupta, Utsav Malviya, Vinod Kapse, "A novel approach to design high speed arithmetic logic unit based onancient vedic multiplication technique", International Journal of Modern Engineering Research, Vol. 2, no. 4, July, 2012, pp 2695 – 2698.

[6] S.P.Pohokar, R.S.Sisal, K.M.Gaikwad, M.M.Patil, Rushikesh Borse, "Design and Implementation of 16 x 16Multiplier Using Vedic Mathematics", Proc of International Conference on Industrial Instrumentation and Control (ICIC), IEEE, 28-30 May 2015.

[7] Abhyarthana Bisoyil, Mitu Baratl, Manoja Kumar Senapati, "Comparison ofa 32-Bit Vedic Multiplier With AConventional Binary Multiplier", Proc of IEEE International Conference on Advanced Communication Control and Computing Technologies (ICACCCT), 8-10 May 2014, pp 1757 – 1760.

[8] H.G. Rangaraju, U. Venugopal, K.N.

Muralidhara, K.B. Raja, Low power reversible parallel binary adder/subtractor, International Journal of Scientific and Engineering Research,1(3), 2010, 23–34.

[9] A. Peres, Reversible logic and quantum computers, Physical Review, 32(6), 1985, 3266–3267.

[10] R. Feynman, Quantum mechanical computers, Foundations of Physics, 16(6), 1986, 507–531.

[11] M. Haghparast, S.J. Jassbi, I.K. Navi, and O. Hashemipour, Design of a novel reversible multiplier circuit using HNG gate in nanotechnology, World Applied Sciences Journal, 3(6), 2008, 974–978.E.

[12] Fredkin and T. Toffoli, Conservative logic, International Journal of Theoretical Physics, 21, 1980, 219– 53.