# Design of 512-Bit Ladner Fishner Adder

K.Sinduja <sup>[2]</sup>S.M.Dinesh <sup>[3]</sup>M.Vinisha <sup>[4]</sup>N.Devi Priya

<sup>[1]</sup> Department of ECE,

SNS College of Technology,

Coimbatore, Tamil Nadu, India.

*Abstract:* To make addition operations additional economical parallel prefix addition may be a higher technique. during this paper 64-bitparallel prefix addition has been enforced with the assistance of cells like black cell and gray cell operations for carry generation and propagation. This method offers high speed computations with high fan-out and makes carry operations easier. ISE Design suit 14.5 tool has been used for the simulation of projected 512-bit adder. The comparison are often created with the help numerous vary of inputs conjointly. The projected parallel prefix adder has made high speed computation and also efficient in terms of range of transistors and their topology and range of nodes.

## I. INTRODUCTION

In information processing system style adder is a very important component and it's employed in multiple blocks of its architecture. In several Computers and in numerous categories of processor specialization, adders don't seem to be solely employed in Arithmetic Logic Units, however conjointly wont to calculate addresses and table indices. There exist multiple algorithms to carry on addition operation starting from straightforward Ripple Carry Adders to complicated CLA.

The fundamental operations concerned in any Digital Signal Processing systems area unit Multiplication, Addition and Accumulation. Addition is an indispensible operation in any Digital, DSP or system. thus quick and correct operation of digital system depends on the performance of adders. thus rising the performance of adder is the main space of analysis in VLSI system style. Over the last decade many alternative adder architectures were studied and planned to hurry up the binary additions. the main points of Ripple Carry Adder and Carry choose Adder area unit, and also the implementation of planned system is described below. The performance and simulation results were conferred and mentioned in section IV.

## II. RIPPLE CARRY ADDER:

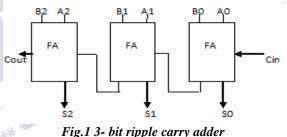

The Ripple Carry Adder is employed to cipher addition of 2N-bit numbers. It consists of N full adders to feature N-bit numbers. From the second full adder, carry input of each full adder is that the carry output of its previous full adder. This kind of adder is often referred to as Ripple Carry Adder because carry ripples to next full adder. The layout of Ripple Carry Adder is easy, that permits quick style time. The Ripple Carry Adder is slowest among all the adders as a result of each full adder should wait until the previous full adder generates the carry bit for its input. The 3-bitRCA is shown in Figure one. on paper the Ripple Carry Adder has delay of o(n) and space of o(n).

# III. CARRY SELECT ADDER (CSLA)

In physical science, carry-select adder may be a specific thanks to implement Associate in nursing adder. It's a electronic device that computes the sum of 2 n-bit numbers. The carry-select adder usually composes of 2 ripple carry adders and a electronic device. The Carry chooses Adder consists of twin Ripple Carry Adders and a electronic device. The changed CSLA is shown in Figure three. In this diagram the addition of 2 16-bit numbers is finished with 2RCA of cin=0 and cin=1. After the calculation for 2 cases of carry, the proper add as well as correct carry is chosen by mistreatment electronic device once the correct carry is understood. There ar2styles of Carry choose Adders one is uniform and another one is variable carry choose adder . In uniform Carry choose Adder every block size is mounted all told stages, but in variable Carry choose Adder block size is variable. The delay at cin input stage may be reduced mistreatment variable sort of CSLA. on paper delay and

Carry space of choose Adder ar  $o(\sqrt{n})$  and o(2n) severally.

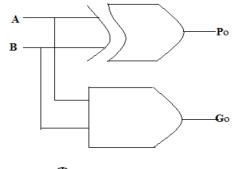

## **IV. CELLS LOGIC DIAGRAMS**

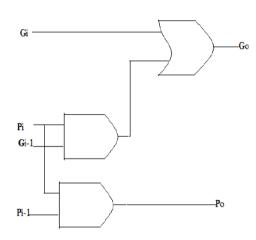

1. Black Cell:

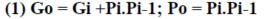

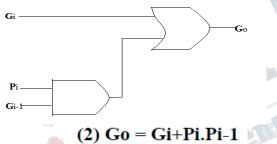

2. Grey cell:

$$(2) Go = Gi + Pi.Pi-1$$

3. White Cell:

(3)  $Po = A \bigoplus B = AB \Box + A \Box B Go = AB$ V. LADNER-FISCHER ADDER:

Ladner-Fischer adder may be a parallel prefix variety of Carry Look-ahead Adder. Ladner-Fischer adder [14] will be represented as a parallel prefix graph consisting of carry operator nodes. The time needed to come up with carry signals in this prefix adder is o(log n). it's the quickest adder with focus on style time and is that the common alternative for top performance adders in business. The Ladner-Fischer adder concept was developed by R. Ladner and M. Fischer [14], which was printed in 1980. the higher performance of Ladner-Fischer adder is owing to its minimum logic depth and finite fan-out. On the opposite facet it occupies giant silicon space.

## VI. PROPOSED LADNER FISCHER ADDER

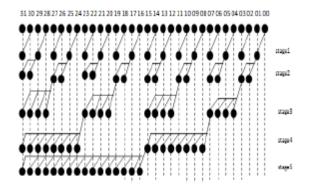

The Ladner-Fischer adder projected is for 512 bit. It is versatile to hurry up the binary addition and therefore the structure seems like tree structure forth high performance of arithmetic operations. In ripple carry adders every bit watch for the last bit operation. In parallel prefix adders rather than looking ahead to the carry propagation of the primary addition, the concept here is to overlap the carry propagation of the primary addition with the computation in the second addition, so forth, since repetitive additions will be performed by a multi operand adder. Research on operation parts and motivation offers development of devices. Field programmable gate arrays [FPGA's] are hottest in recent years as a result of they improve the speed of chip based mostly applications like mobile DSP and telecommunication. the development of efficient Ladner-Fischer adder consists of 3 stages. They are pre-processing stage, carry generation stage, post-processing stage.

Fig.2-.3bit LF adder

#### Fig.3-.32bit LF adder

## VII. PRE PROCEESING STAGE:

In the pre-processing stage, generate and propagate square measure from each combine of inputs. The propagate provides "XOR" operation of input bits and generates provides "AND" operation of input bits. The propagate (Pi) and generate (Gi) square measure shown in below equations four &five.

| $P_i = A_i \oplus B_i$ (1)                        | ) |

|---------------------------------------------------|---|

| G <sub>I</sub> =A <sub>i</sub> .B <sub>i</sub> (2 | ) |

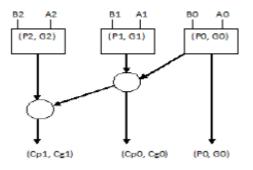

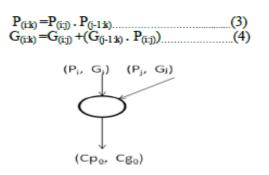

## VIII. CARRY GENERATION STAGE:

In this stage, carry is generated for every bit and this can be known as carry generate (Cg). The carry propagate and carry generate is generated for the additional operation however final cell gift in the every bit operation provides carry. The last bit carry can facilitate to produce total of succeeding bit at the same time until the last bit. The carry generate and carry propagate square measure given in below equations half-dozen & seven. The on top of carry propagate Cp and carry generation Cg in equations 6&7 is black cell and therefore the below shown carry generation in equation eight is grey cell. The carry propagate is generated for the additional operation however final cell gift within the each bit operation provides carry. The last bit carry canfacilitate to produce total of succeeding bit at the same timeuntil the last bit. This carry is employed for succeeding bit total operation, the carry generate is given in below equations eight.

#### **IX. POST PROCEESING STAGE:**

It is the ultimate stage of associate degree economical Ladner-Fischer adder, the carry of a primary bit is XORed with consecutive little bit of propagates then the output is given as add and it's shown in equation nine. It is used for 2 sixteen bit addition operations and every bit carry is undergoes post-processing stage with propagate, gives the final add. The first input bits goes beneath pre-processing stage and it'll produce propagate and generate. These propagates and generates undergoes carry generation stage produces carry generates and carry propagates, these undergoes post-processing stage and offers final add. The step by step method of economical Ladner-Fischer adder is shown in Fig one. The economical Ladner-Fischer adder structure is trying like tree structure for the high performance of arithmetic operations and it's the quickest adder that focuses on gate level logic. It styles with less variety of gates. So, it decreases the delay and memory employed in this design. In economical Ladner-Fischer adder, black cell operates 3gates and grey cell operates 2 gates. the grey cell reduces the delay and memory as a result of it operates solely 2 gates. The proposed adder is style with the each black and grey cells. By mistreatment grey cell operations at the last stage of projected adder provides a large dropping delay and memory used. The projected adder is shown in fig a pair of that improves the speed and reduces the memory for the operation of 8-bitaddition. The input bits Ai and metallic element concentrates on generate and propagate by XOR and AND operations. These propagates and generates undergoes the operations of black cell and grey cell and offers the carry Ci. That carry is XORed with the propagate of next bit, that provides add. The design of economical Ladner-Fischer adder provides the less delay and fewer memory for the operation of 16-bitaddition. The properties of the operations square measure evaluated in parallel and settle for the trees to overlap that results in parallelization. The design of 16-bit economical Ladner-Fischer adder is shown in Fig three. The logical circuit is mistreatment multiple adders to N find the

add of N-bit numbers. every addition operation incorporates a carry input (Cin) that is that the previous bit carry output (Cout). The economical Ladner-Fischer Adder style takes less variety of gates. Typically every black cell consists of 2 AND gates, one logic gate and grey cell consists of 1 AND gate. one OR gate. The last stage style with the gate level logic with the gray cell reduces delay and memory. Research on binary addition motivates provides development of devices. several parallel prefix networks describe the literature of addition operation. The parallel prefix adders square measure Brent-kung, Kogge-stone, ladner-Fischer, Sklansky, etc. The quick and correct performance of associate degree adder is employed within the terribly massive scale integrated circuits style and digital signal processors. The economical Ladner-Fischer adder is intended on VHDL(very high speed integration hardware description language). Xilinx project navigator twelve.1 is employed for synthesis. Simulation results square measure.

$S_i = P_i \bigoplus C_i$ (5)

$$C_{i+1} = (P_i \bullet C_0) + G_{i...}$$

X. CONCLUSION

.(6)

In this paper, a brand new approach to style AN economical Ladner-Fischer adder concentrates on gate levels to boost the speed and decreases the memory. it's like tree structure and cells in the carry generation stage are attenuated to hurry up the binary addition. The projected adder addition operation offers nice advantage in reducing delay.

Fig .5-Simulation output for ladner fishner 512-bit.

## **REFERENCES:**

[1] Pakkiraiah. Chakali, madhu Kumar. Patnala "Design of high speed Ladner - Fischer based carry select adder" IJSCE march 2013

[2] Haridimos T.Vergos, Member, IEEE and Giorgos Dimitrakopoulos, Member, IEEE," On modulo 2n+1 adder design" IEEE Trans on computers, vol.61, no.2, Feb 2012

[3] B. Ramkumar, Harish M Kittur, "Low –Power and Area-Efficient Carry Select Adder", IEEE transaction on very large scale integration (VLSI) systems, Feb 2012.

[4] P.Ramanathan' P.T.Vanathi' "Novel Power Delay Optimized 32-bit Parallel Prefix Adder for High Speed Computing"' International Journal of Recent Trends in Engineering' Vol 2' No. 6' November 2009.

[5] Vikramkumar Pudi and K. Sridharan, "Efficient Design of a Hybrid Adder in Quantum-Dot Cellular Automata,"IEEE Trans., Very Large Scale Integr. (VLSI) Syst., Vol. 19, no. 9, Sep. 2011.

[6] D. H. K. Hoe, C. Martinez, and J. Vundavalli, "Design and Characterization of Parallel Prefix Adders using FPGAs, "IEEE 43rd Southeastern Symposium on System Theory, pp. 170-174, March 2011.

tree uated lition