# Implementation of Logic Circuits with Low Energy Charge Recovery Logic

<sup>[1]</sup> Deepak Mittal, <sup>[2]</sup> Anjan Kumar

<sup>[1][2][3]</sup> Institute of Engineering and Technology, Electronics and Communication Department, GLA University, Mathura Uttar Pradesh, India

*Abstract* - Various energy recovery circuits have been proposed for reducing the power dissipation in CMOS logic circuits. This paper presents three Logic Circuits implemented using charge recovery logic. They are completely unique boost logic known as pseudo-NMOS boost logic (PNBL), to get low energy consumption and efficient-speed as compare to CMOS binary logic. PNBL is faster and compact charge recovery logic and it related to boost logic family. These logic circuits have less operating energy dissipation due to charge recovery logic. To exhibit the performance of Logic circuits are implemented with PNBL and compared with CMOS in 180nm technology. Simulation results show that logic circuits with PNBL recover the charge 57.14nJ at the frequency of 1GHZ that is approximately 105 times conserve energy as compared to conventional CMOS technology. Charge recovery logic also has one more advantage that it provided complemented and non-complemented both output at a time with small area trade-off.

Index Terms: Pseudo N-MOS Boost Logic, Low Energy Consumption, Charge recovery logic, Adiabatic Logic.

### I. INTRODUCTION

Today scenario in VLSI design energy dissipation is one of the most prominent issues. Energy dissipation may be essential factor because of the disability to get back the power from the circuit. Charge recovery logic can get back the energy from the circuit so this technique is used because of its energy conservation. [1]

In many literatures the Charge recovery logic represented smart work over low energy as a result of circuit energy is preserved rather than consumption as heat. But the one trade-off is finding between power dissipation and performance. [2]

Variety of things such as threshold voltage and transition rate will have an effect on the energy efficiency of charge recovery logic, so this factor can affect the performance of the circuitry. But boost logic operates with less energy consumption as compare to  $CV^2/2$  that is the usual energy consumption of CMOS based circuit [3].

Charge recovery logic's in ref. [4] toughly work correctly only when the operating frequency of these circuits increases. Charge recovery logic uses two phase logic that consists of energy recovery stages with conventional switches which can achieve significant energy. [5]

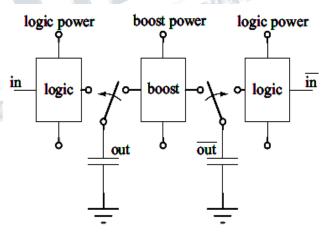

For boost logic, when the power clock is lesser a waiting status exists, the circuits are idle for half cycle of power

clock so that the operation performance is not allowed. Fig. 1 shows the working principle of boost logic family. [6]

Fig.1. Boost logic family basic operation

In first step logic values measures within the logic block and in second step this logic value boosted to higher voltage using the boost block. Boost logic is used in synchronous sequential circuits so this structure can be divided into two parts so boost logic will operated by power clock. In this research paper, charge recovery logic referred to as PNBL designed. Boost logic's PNBL technique is highly drivable as compare to other logics. For certify the effect of PNBL in decreasing energy consumption of logic circuits compared to conventional CMOS logic circuits with the more area trade off. [7]

#### II. PSEUDO NMOS BOOST LOGIC

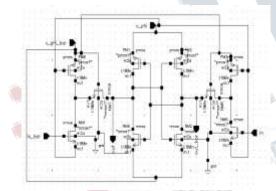

In this research paper, operations of Pseudo- NMOS Boost Logic are implemented. In these circuits without overlapping intervals clock and clock bar are used so DC power is not used in PNBL. In PNBL circuits PUNs in each rail are replaced with one PMOS transistor and gates are connected with clock of the PMOS transistors. PNBL uses less number of transistors so that the input capacitances of PNBL are smaller. In the sequential circuits; the input capacitance of one gate is the load capacitance of another PNBL gates so the major power consumption is due to load capacitance in PNBL circuits. Clock is in high voltage whereas clock bar is in lower voltage in the analysis stage. When clock bar is low, PMOS PM0 and PM2 behave as Pull-Up Network and makes pull up network always on, and therefore the complementary inputs make one Pull down network and makes pull down network always on. In pseudo-NMOS circuits same methodology is used. In Pseudo Boost logic (PBL) threshold voltage loss does not exists because PMOS transistor uses for pull up the logic is in always high state. [8]

In the operation of Pseudo NMOS Boost logic (PNBL) throughout this operation, pass gates NM7 and NM8 will be on since clock is high. Voltage created by the charge recovery block will hardly affect these values, in the analysis stage. In the charge recovery stage, clock bar will be in low half cycle whereas clock will be in high half cycle. Pass gates NM7 and NM8 are each off when the clock bar is low.

Initially Input 'in' is high and 'in\_bar' is low so the NM1 becomes off and NM5 becomes on. V\_phi is low so PM3 and PM5 are on and at the same time V\_phi\_bar is high so NM7 and NM8 are on. So the Out is initially high and Out\_bar is initially high but it becomes high to low through the path of NM8 to NM5. So that we have been achieved the boosted out and out\_bar both in the same time. This operation vice versa is also true.

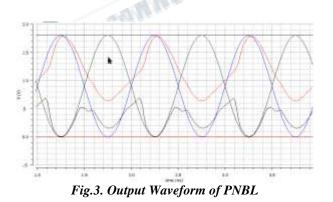

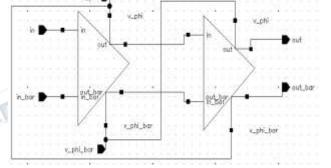

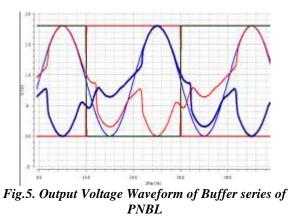

Fig. 4 shows the buffer series of PNBL and Fig.5 shows the output wave of PNBL gates buffer1 and buffer2. In this circuit output of first stage is the input of second stage. Each buffer internal operation is same as previously explained circuit of PNBL.

Fig.2. Structure of PNBL

Fig.4. Buffer series of PNBL

## III. IMPLEMENTATION OF DIFFERENT LOGIC CIRCUIT OF PNBL

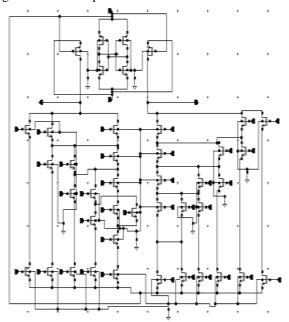

5-bit comparator schematic using PNBL is shown in Fig.6.

In this schematic upper part shows the boost circuit and below left part shows the Pull up network and right part shows the pull down network of the 5-bit comparator circuit. Interesting fact is for both pull up and pull down network NMOS transistor is used. Because in PNBL circuits boost block circuit act as pull up network and logic circuit act as pull down network.

Fig.6. 5-bit comparator schematic

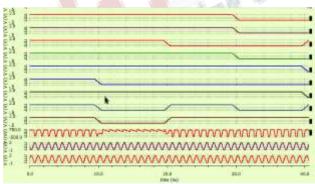

Fig.7. Output Waveform of 5-bit comparator schematic

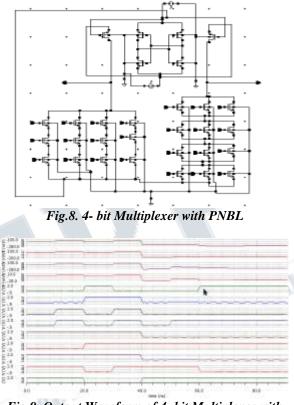

Schematic of 4-bit PNBL multiplexer is shown below in Fig.8. In this circuit pull up network and pull down

network shows out and out bar respectively. So it can drive more than one function at a time.

Fig.9. Output Waveform of 4- bit Multiplexer with PNBL

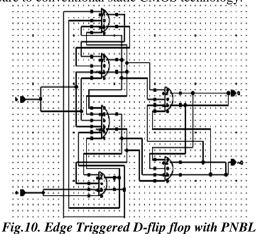

Following schematic shows the Edge triggered D Flipflop with PNBL. This provides the more functionality with less power dissipation with small area trade off as compare to conventional static CMOS technology.

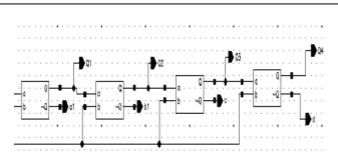

Fig.11. 4-bit Accumulator Register with PNBL

Fig.12. Output Waveform of 4-bit Accumulator Register with PNBL

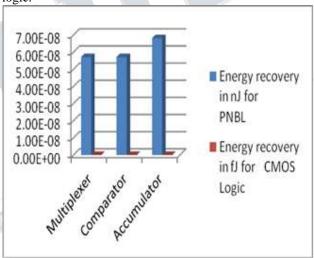

**IV. SIMULATION RESULTS AND DISCUSSION** Compare the energy recovery against the pseudo NMOS boost logic represented by Multiplexer, Comparator and Accumulator register. Energy recovery of different logic circuit is given below

### I. Energy recovery of different logic circuits with PNBL compared with CMOS logic circuits

| Name of the logic<br>circuit | Energy recovery in<br>nJ for PNBL | Energy recovery in fJ<br>for CMOS Logic |

|------------------------------|-----------------------------------|-----------------------------------------|

| Multiplexer                  | -57.14                            | -703.3                                  |

| Comparator                   | -57.14                            | -709.1                                  |

| Accumulator                  | -68.12                            | -706.4                                  |

All the values are negative that means it shows the energy recovery not the energy dissipation. Energy recovery of pseudo NMOS Boost Logic based Multiplexer; Comparator and Accumulator register is much more compare to the energy recovery of the conventional CMOS based logic. Charge recovery of conventional CMOS Logic is approximately negligible. This energy recovery is approximately 105 times more with high speed with trade off. Numbers of used transistors are more in PNBL based logic circuits compared to the conventional CMOS based logic circuits. Because in the PNBL implemented one extra Boost logic circuit in place of PMOS which reduces the number of transistors but for Boost Logic circuit we needed complementary and non complementary circuit so that number of transistors we needed more compare to the conventional CMOS based logic.

| II. Area consumption | of logic circuits with PNBL |

|----------------------|-----------------------------|

| compared with        | CMOS logic circuits.        |

| Name of the<br>Logic circuit | Total Number used of<br>Transistors used for<br>PNBL | Total Number of<br>Transistors used for<br>CMOS Logic |

|------------------------------|------------------------------------------------------|-------------------------------------------------------|

| Multiplexer                  | 42                                                   | 72                                                    |

| Comparator                   | 42                                                   | 36                                                    |

| Accumulator                  | 248                                                  | 184                                                   |

|                              |                                                      |                                                       |

# International Journal of Engineering Research in Computer Science and Engineering (IJERCSE)

# Vol 5, Issue 2, February 2018

#### CONCLUSION

In this paper pseudo NMOS Boost logic based Logic circuits are proposed. Comparing with conventional CMOS based Logic circuits. The projected PNBL based logic circuits conserve approximately 81250 times energy compared to the conventional CMOS based logic circuits with small area trade off.

### REFERENCES

[1] Y. Zhang, L. Okamura, and T. Yoshihara, "An energy efficiency 4-bit multiplier with two-phase nonoverlap clock driven charge recovery logic," Electronics, IEICE Transactions on, vol. E94-C, no.4, pp. 605–612, April 2011.

[2] J. C. Kao, W. H. Ma, V. S. Sathe, and M. Papaefthymiou, "Energy efficient low-latency 600 mhz fir with high-overdrive charge recovery logic," Very Large Scale Integration (VLSI) Systems, IEEE Transactions on, vol. PP, no. 99, pp. 1–12, 2011.

[3] Cihun-Siyong Alex Gong, Muh-Tian Shiue, Ci-Tong Hong, and KaliWenYao, "Analysis and Design of an Efficient Irreversible Energy Recovery Logic in 0.18 m CMOS," IEEE Trans. Circuits Syst. I,vol .55, No.9, pp.2595-2607, Oct. 2008.

[4] V. S. Sathe, J. Y. Chueh, and M. C. Papaefthymiou, "Energy-efficient ghz-class charge-recovery logic," Solid-State Circuits, IEEE Journal of, vol. 42, no. 1, pp. 38–47, Jan. 2007.

[5] Changning Luo and Jianping Hu, "Single-phase adiabatic flip-flops and Sequential circuits using improved CAL circuits," IEEE ASICON'07,Guilin, China, pp. 126-129, 2007.

[6] D. Suvakovic and C. Salama, "Two phase nonoverlapping clock adiabatic differential cascade voltage switch logic (adcvsl)," Solid-State Circuits Conference, 2000. Digest of Technical Papers. ISSCC. 2000 IEEE International, pp.364–365, 2000.

[7] Y. Moon and D-K. Jeong, "An efficient charge recovery logic circuit", IEEE Solid-State Circuits, vol. 31, no. 4, pp.514-522, Apr. 1996.

[8] Y. Ye and K. Roy, "quasi-static energy recovery logic," Solid-State Circuits, IEEE Journal of, vol. 36, no. 2, pp. 239–248, Feb. 2001.

[9] Y. Takahashi, K. Konta, K. Takahashi, M. Yokoyama, K. Shouno, and M. Mizunuma, "Carry propagation free adder/subtracted using adiabatic dynamic emos logic circuit technology," Fundamentals of Electronics, Communications and Computer Sciences, IEICE Transactions on, vol.E86-A, no.6,pp. 1437–1444, Jun 2003.

[10] V. De and J. Meindl, "Complementary adiabatic and fully adiabatic mos logic families for giga scale integration," Solid-State Circuits Conference, 1996. Digest of Technical Papers. 42nd ISSCC, 1996 IEEE International, pp. 298–299, 461, Feb. 1996.

[11] Y. Takahashi, T. Sekine, and M. Yokoyama, "VLSI implementation of a 4x4-bit multiplier in a two phase drive adiabatic dynamic CMOS logic," Electronics, IEICE Transactions on, vol. E90-C, no. 10, pp. 2002– 2006, Oct 2007.