Vol 4, Issue 8, August 2017

# REDUCING LEAKAGE POWER IN CMOS CIRCUITS

[1] Arul V

<sup>[1]</sup> Department of Electronics and Communication Engineering, Galgotias University, Yamuna Expressway Greater Noida, Uttar Pradesh

[1] v.arul@galgotiasuniversity.edu.in

Abstract: Later Technological advances in Wireless Communication has demonstrated the union of terminals and, arranges that help interactive media for continuous applications. This clearly puts a massive weight on battery of any cell phone. The CMOS has been the main innovation in this age of portable correspondence because of its low force utilization. Decrease of leakage power in CMOS has been the examination enthusiasm for the most recent few years. In CMOS coordinated circuit structure there is a significant exchange off between innovation scaling and static force utilization. In the present CMOS innovation the leakage power utilization assumes a noteworthy work. While getting closer to Nano-scale plan the complete chip power utilization becomes reliant on leakage power. Expanding the battery life in versatile remote correspondence and portable registering also, comparable different applications is the subject of research now-a day's... Further, since the leakage of battery exists even at the point when gadgets are out of gear state makes leakage power misfortune generally basic in CMOS VLSI circuits. Numerous systems have been advanced to handle the issue which is still in progress. This paper centres on the audit of different works done in this field till the present date.

Keywords: Wireless communication, CMOS, Leakage power, Nano-scale, VLSI, Transistor circuit.

#### INTRODUCTION

The fast development in semiconductor innovation through the utilization of profound submicron forms has driven the component sizes to contract; in this manner incorporating incredibly complex usefulness on a single chip. In the ever expanding business sector of portable hand-held gadgets utilized all over the present reality, the batterycontrolled electronic framework shapes the spine. To augment the battery life, the huge computational limit of versatile gadgets for example, journal PCs, individual correspondence gadgets (cell phones, PDAs, pocket PCs) portable hearing assistants and implantable pacemakers must be acknowledged with very low force necessities.

The power dissipation has become an exceptionally basic structure metric because of gadget scaling

down and fast development towards remote correspondence. The more extended the battery

keeps going; the better is the gadget. The power dissipation has not lessened even with the downsizing of the supply voltage [1]. The issue of warmth expulsion and force scattering is deteriorating as the extent of intensity per unit zone has continued developing. There is a little assistance from cutting edge cooling and packaging systems the fast increment in power utilization of present day chips. Although, the expense related with the bundling and the cooling of such gadgets is getting restrictive. Notwithstanding cost, the issue of unwavering quality is a significant concern. It is as of now announced that Component disappointment rate generally duplicates for each 10°C increment in working temperature. Following Moore's law, with the on-chip gadgets multiplying each two a long

Vol 4, Issue 8, August 2017

time, limiting the force utilization has become right now an incredibly testing zone of research.

Leakage intensity of a CMOS transistor relies upon door length and oxide layer thickness. To diminish the dynamic power, the stock voltage is diminished which prompts the execution corruption [2]. To speed up the gadget, the edge voltage ought to likewise be scaled down alongside the stockpile voltage, which results in exponential increment in the sub-limit leakage current, in this manner increment in the static force dissemination. With the expansion in the leakage current to an ever increasing extent, as will be seen that it gets corresponding to the aggregate power dispersal as given by following condition. In this age there is an immense interest for limiting the dynamic force dispersal and downsizing the supply voltage by pushing the circuit's structure towards regularly shortening divert lengths in CMOS innovation. To keep up the circuit speed, the transistor edge voltages should likewise be downsized. This can be effectively seen from the primary request producing defer condition of a transistor given by following condition.

$$\tau = \frac{C \ V dd}{\left(V dd - Vt\right)^{x}}$$

Where C is the heap capacitance,  $V_t$  is the edge voltage; x (which is more prominent than 1 yet under 2) models the short channel impact. The sub edge leakage current exponentially increments as Vt is diminished. This guideline of sub edge current is trailed by the majority of the procedures for low leakage power. It has been indicated that as the innovation downsizes underneath 100nm which is the contracting of highlight size of transistor, the channel length diminishes, in this manner expanding the measure of leakage power in the absolute force disseminated. As should be obvious as the innovation is moving towards lower nanotechnology the sub-limit leakage increments in this manner influencing the battery life. Subsequently there were different strategy created to manage this issues. The

different strategies will be examined in the following segment alongside their disadvantages.

#### **RELATED WORKS DONE**

Numerous strategies have been appeared to defeat the leakage power issue in the Nano-scale innovation, however those strategies have trade-off between territory, delay and furthermore dynamic force. A portion of those systems are as portrayed in this area.

#### 1. Double Vt and MTCMOS

This was the most punctual proposed method to lessen the leakage power. As expressed in Dual VT procedure is a variety in MTCMOS, in which the doors in the basic way utilize low-edge transistors and high-limit transistors for doors in non-basic way[3]. As per the creators both the techniques requires extra cover layers for each estimation of Vt in manufacture, which is a confounded assignment storing two distinct oxides thickness, henceforth making the manufacture procedure complex. Additionally the systems likewise experience the ill effects of turning-on dormancy i.e., the inert of circuit can't be utilized following reactivated since at some point is expected to come back to ordinary working condition. The lifelessness is ordinarily a couple of cycles for previous technique, and for Dual innovation, is a lot higher. When the circuit is dynamic, these procedures are not powerful in controlling the leakage power.

#### 2. Rest Mode Approach

This strategy was created to defeat the pullbacks of the double  $V_t$  and MTCMOS system [4]. As indicated it is one of the most usually known customary methodologies for sub edge leakage power decrease is the rest approach. In this rest approach, extra transistors (rest transistors) are embedded in between the force supply and ground.

Vol 4, Issue 8, August 2017

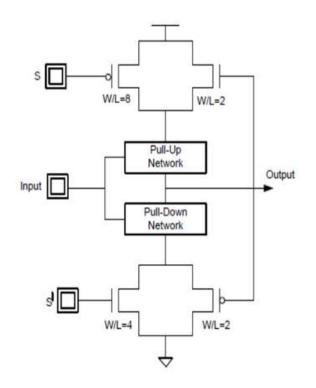

As clarified in this procedure an extra "rest" PMOS transistor is set among VDD and the pull-up system of a circuit and an extra "rest" NMOS transistor is set between the pull down system of the circuits and GND. These rest transistors turn off the circuit by removing the force rails. The rest transistors are turned on when the circuit is dynamic and give low opposition in the conduction way with the goal that circuit's exhibition won't get influenced due to these extra transistors. During the standby mode the leakage power is decreased in the circuit by switching off the transistors which presents enormous opposition in the conduction way. Along these lines leakage force can be decreased viably by turning off the force source. These sorts of systems are additionally called gated-VDD and gated-GND.

#### Figure 1: Sleepy Keeper Approach

#### 3. Stack Approach

The rest strategy however end up being superior to double  $V_t$  and MTCMOS strategy yet anyway proved unable give a wonderful outcome in

lessening the leakage power [5]. This prompted the creators to structure another better circuit and, in this race they recommended another method called the stack procedure which powers a stack impact by breaking down a current transistor into two half size transistors. The creators in their work clarified the ideas behind the structure proposed. It is indicated that prompted switch predisposition between the two transistors results when the two transistors are killed together coming about in subthreshold leakage current decrease. In any case, the disadvantage is increment delay altogether between isolated transistors which could confine the convenience of the methodology.

#### 4. Sleepy Keeper Approach

The creators have clarified the different issues looked by ordinary CMOS circuit. They expressed that the fundamental issue with customary CMOS is that the transistors are utilized distinctly in their generally productive, and, normally modifying, i.e., PMOS transistors are associate to VDD and the NMOS transistors are associate with GND [6]. It is a verifiable truth that the PMOS transistors are most certainly not effective at passing GND and that the NMOS transistors are not effective at passing VDD. Be that as it may, to keep up a estimation of '1' in rest mode, given that the '1' esteem has as of now been determined, the drowsy attendant methodology employments this yield estimation of '1' and a NMOS transistor associated to VDD to keep up yield esteem equivalent to '1' when in rest mode. To handle this issue the creators proposed another structure utilizing unenergetic manager approach in which an extra single NMOS transistor put in parallel to the pull-up rest transistor interfaces VDD to the pull up circuit. When in rest mode, this NMOS transistor is the just wellspring of VDD to the pull up network since the rest transistor is off. An extra single PMOS transistor put in parallel to the pull down rest transistor is the just wellspring of GND to the pull down system [7]. Anyway it was accounted for that significant weakness confronted by this system was the decrease of intensity by less rate

Vol 4, Issue 8, August 2017

which was not ready to satisfy the current requests of present pre-requisite of the VLSI structured circuits.

#### 5. LECTOR Technique

This is one of the low force maintenance systems. The creators proposed a CMOS circuit in which two additional Leakage Control Transistors (a P-type furthermore, a N-type) is embedded inside the door, in which the entryway terminal of every Leakage Control Transistor is constrained by the wellspring of the other. The essential thought behind their methodology was for decrease of leakage power is the successful stacking of transistors in the way from supply voltage to ground. The creators mentioned an objective fact that "a state with more than one transistor are OFF in a way from supply voltage to ground is far less flawed than a state with as it were one transistor OFF in any stock to ground way." In their strategy they presented two leakage control transistors (LCTs) in each CMOS entryway with the end goal that one of the LCTs is close to its cut off locale of activity [8]. They outlined that their Leakage Control Transistor method (LECTOR) with the instance of a NAND entryway .A CMOS NAND door with the expansion of two leakage control transistors. LSSR (Lector Stack State Retention Method).

The primary point of this paper is to survey the works being done on this way to deal with accomplish low force in VLSI circuits. In request to accomplish low force they framed this new circuit configuration by consolidating two recently done methodologies to be specific LECTOR approach and Forced stack approach [9]. Since it consolidates the two previously mentioned systems it has the highlights of both the methodologies and accordingly is a lot advantageous than the past works done. The creators have proposed the circuit by presenting two gated leakage transistors between pull up and, pull down systems with high edge voltage, and at that point stack impact is added to pull up and pull down arranges by partitioning every transistor in to half measure transistors. According

to the works being in progress the creators accept this new method LSSR can be end up being a lot superior to anything the prior works done as indicated by LSSR which can accomplish better leakage decrease by keeping up definite rationale state (state maintenance) than the other procedures [10].

#### CONCLUSION

The principle of this paper was to give a survey of the different advances taken towards the decrease of the leakage power for VLSI structures. A significant push towards the low power structure of CMOS is in reality because of later innovative advances in remote correspondence since the usable time of a cell phone is intensely confined by its battery life. With the developing unpredictability of cell phones, for example, with an advanced camera, sight and sound administrations, Video Conferencing, "Global Positioning system" (GPS) and so on are the highlights which make the battery power issue additionally testing. To take care of the issue confronted different works have been actualized and still experts are dealing with this field. Through this paper a good pace preferences and hindrances of different works done was calculated. LECTOR and the new methodology LSSR circuit may prompt a lot of enormous decrease of leakage power than the stack and rest pulls near. At last it is presumed that the advanced design will likewise play a significant job in lessening the leakages.

#### REFERENCES

- [1] M. V. P. Done, U. Panwar, and K. Khare, 'An algorithmic approach for leakage current reduction in deep sub-micron CMOS circuits', in 2014 International Conference on Advances in Electronics, Computers and Communications, ICAECC 2014, 2015.

- [2] K. J. Kuhn et al., 'The ultimate CMOS device and beyond', in Technical Digest -International Electron Devices Meeting,

Vol 4, Issue 8, August 2017

IEDM, 2012.

- [3] R. Rastogi and S. Pandey, 'Leakage power reduction in MTCMOS based high speed adders', in *IEEE International Conference* on Computer Communication and Control, *IC4 2015*, 2016.

- [4] H. Jiao and V. Kursun, 'Ground-bouncingnoise-aware combinational MTCMOS circuits', *IEEE Trans. Circuits Syst. I Regul. Pap.*, vol. 57, no. 8, pp. 2053–2065, 2010.

- [5] E. N. Shauly, 'CMOS leakage and power reduction in transistors and circuits: Process and layout considerations', *Journal of Low Power Electronics and Applications*. 2012.

- Y. H. Chen *et al.*, 'A 16nm 128Mb SRAM in high-? metal-gate FinFET technology with write-assist circuitry for low-VMIN applications', in *Digest of Technical Papers* - *IEEE International Solid-State Circuits Conference*, 2014.

- [7] B. Hopf, 'Choosing an Appropriate Pull-up / Pull-down Resistor for Open Drain Outputs', *Texas Instruments Appl. Rep.*, 2011.

- [8] T. K. Gupta and K. Khare, 'Lector with footed-diode inverter: A technique for leakage reduction in domino circuits', *Circuits, Syst. Signal Process.*, 2013.

- [9] K. Parat and C. Dennison, 'A floating gate based 3D NAND technology with CMOS under array', in *Technical Digest -International Electron Devices Meeting*, *IEDM*, 2015.

- [10] K. Kumari, A. Agarwal, J. Jayvrat, and K. Agarwal, 'Review of Leakage Power Reduction in CMOS Circuits', Am. J. Electr. Electron. Eng., 2014.

- [11] K Deepika, N Naveen Prasad, S Balamurugan, S Charanyaa, "Evolution of Cloud Computing: A State-of-the-Art Survey", International Journal of Innovative Research

in Computer and Communication Engineering, Vol. 3, Issue 1, January 2015

[12] R. S. Venkatesh, P. K. Reejeesh, S. Balamurugan and S. Charanyaa, "Future Trends of Cloud Computing Security: An Extensive Investigation", International journal of Innovative Research in Computer and Communication Engineering, vol. 3, no. 1, 2015.